- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

SiGe 및 Si 선택적 에칭 기술

FinFET를 대체할 차세대 트랜지스터 아키텍처인 GAAFET(Gate-All-Around FET)는 더 작은 크기에서 뛰어난 정전기 제어와 향상된 성능을 제공하는 능력으로 큰 주목을 받아왔습니다. n형 GAAFET 제조의 중요한 단계에는 높은 선택성이 포함됩니다.에칭내부 스페이서를 증착하기 전에 SiGe:Si 스택을 사용하여 실리콘 나노시트를 생성하고 채널을 방출합니다.

이 기사에서는 선택 항목에 대해 자세히 설명합니다.에칭 기술SiGe 에칭에서 높은 정밀도와 선택성을 달성하기 위한 새로운 솔루션을 제공하는 두 가지 새로운 에칭 방법인 고산화성 가스 플라즈마 프리 에칭과 원자층 에칭(ALE)을 소개합니다.

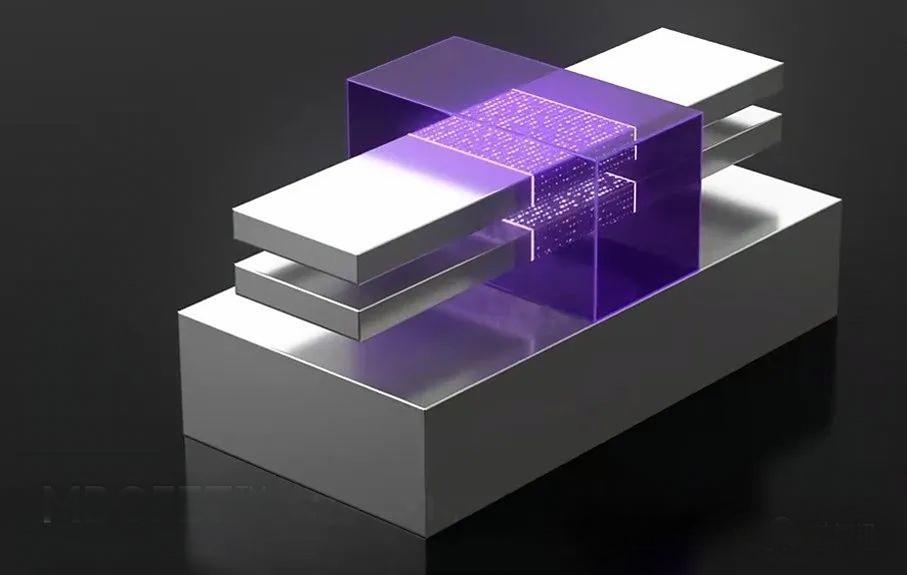

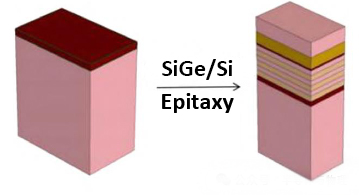

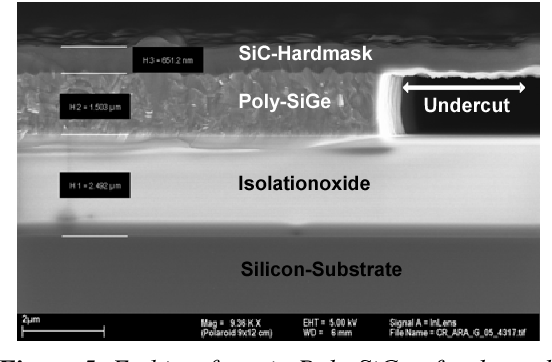

GAA 구조의 SiGe 초격자 층

GAAFET 설계에서는 장치 성능을 향상시키기 위해 Si와 SiGe의 교번 층이 사용됩니다.실리콘 기판 위에 에피택셜 성장, 초격자로 알려진 다층 구조를 형성합니다. 이러한 SiGe 층은 캐리어 농도를 조정할 뿐만 아니라 응력을 도입하여 전자 이동도를 향상시킵니다. 그러나 후속 공정 단계에서 이러한 SiGe 층은 실리콘 층을 유지하면서 정밀하게 제거되어야 하므로 매우 선택적인 에칭 기술이 필요합니다.

SiGe의 선택적 에칭 방법

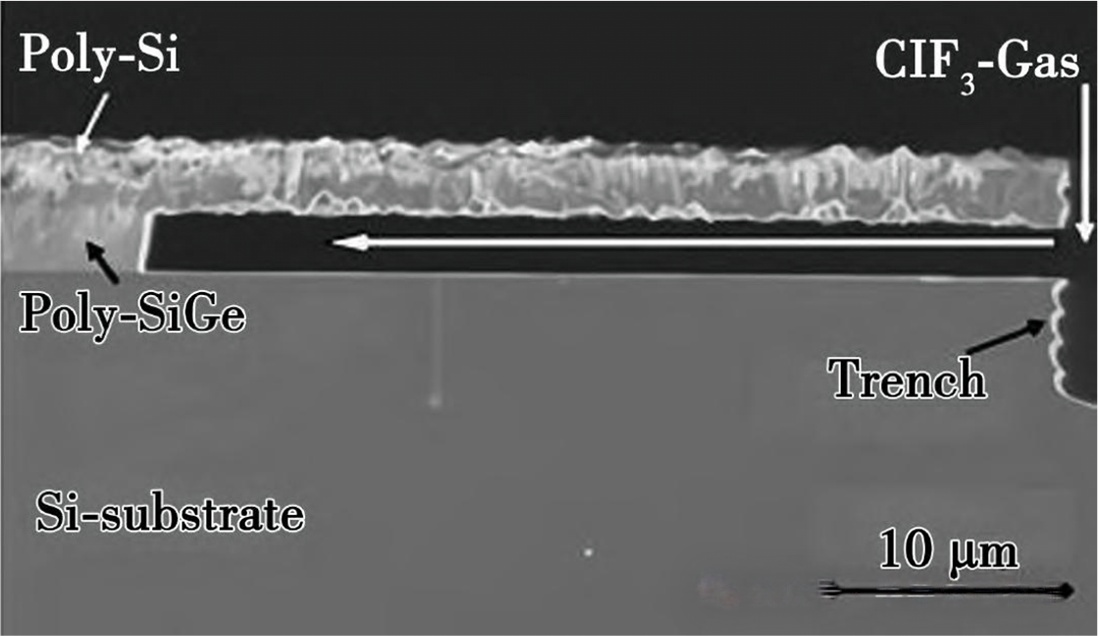

고산화성 가스 플라즈마 프리 에칭

ClF3 가스 선택: 이 에칭 방법은 ClF3와 같이 선택성이 매우 높은 산화성이 높은 가스를 사용하여 1000-5000의 SiGe:Si 선택비를 달성합니다. 플라즈마 손상을 일으키지 않고 상온에서 완료될 수 있습니다.

저온 효율: 최적의 온도는 약 30°C로 저온 조건에서 고선택성 에칭을 실현하여 장치 성능을 유지하는 데 중요한 추가적인 열 예산 증가를 방지합니다.

건조한 환경: 전체에칭 공정완전히 건조한 상태에서 수행되므로 구조물 접착의 위험이 없습니다.

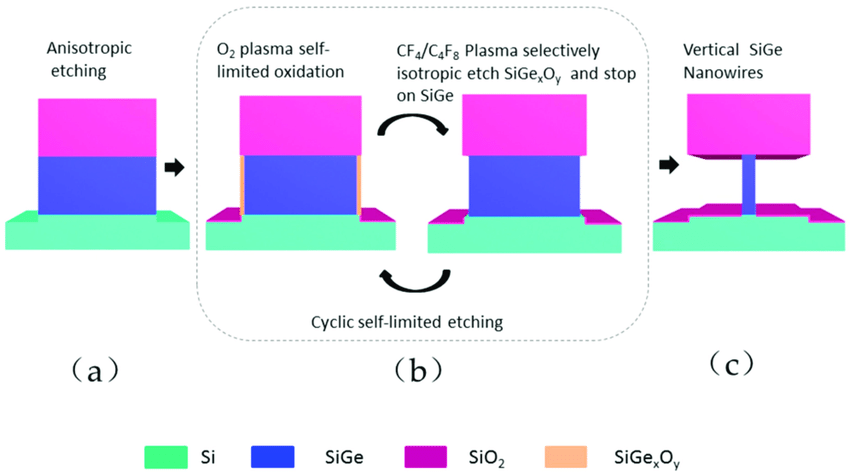

ALE(원자층 에칭)

자체 제한 특성: ALE는 2단계 순환입니다.에칭 기술, 에칭할 재료의 표면을 먼저 수정한 다음 수정되지 않은 부분에 영향을 주지 않고 수정된 레이어를 제거합니다. 각 단계는 자체 제한적이므로 한 번에 몇 개의 원자층만 제거하는 수준의 정밀도를 보장합니다.

주기적 에칭: 앞서 언급한 두 단계는 원하는 에칭 깊이에 도달할 때까지 반복적으로 순환됩니다. 이 프로세스를 통해 ALE는 다음을 달성할 수 있습니다.원자 수준의 정밀 에칭내벽의 작은 구멍에.

Semicorex는 다음을 전문으로 합니다.SiC/TaC 코팅 흑연 솔루션반도체 제조의 Etching 공정에 적용됩니다. 문의 사항이 있거나 추가 세부 사항이 필요하면 언제든지 문의해 주세요.

전화번호: +86-13567891907

이메일: sales@semicorex.com