- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

소식

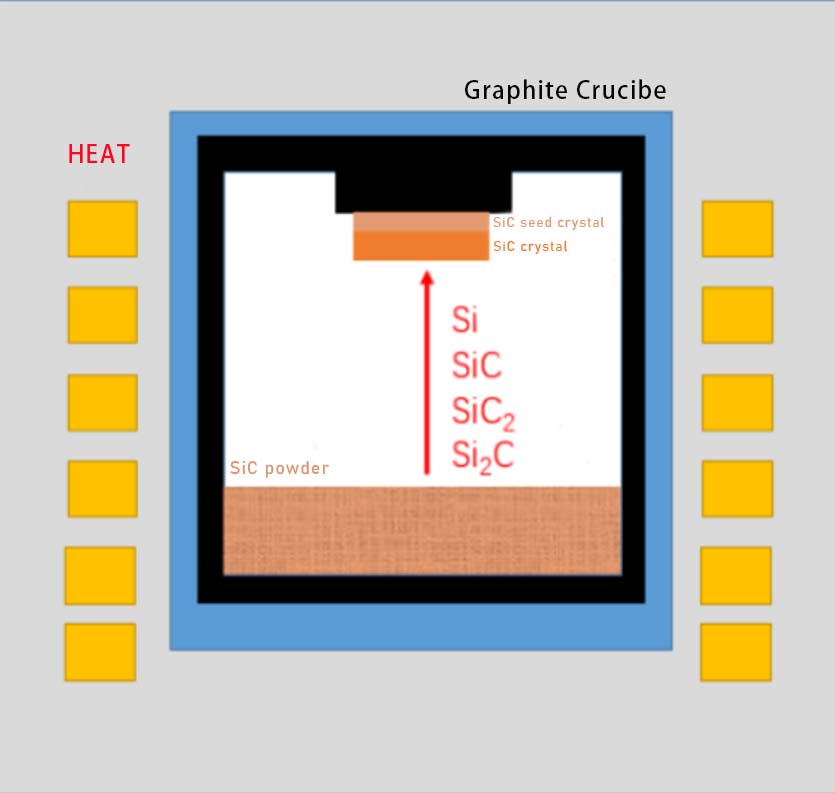

흑연 성형의 3가지 방법

흑연 성형의 네 가지 주요 성형 방법은 압출 성형, 성형, 진동 성형 및 등압 성형입니다. 시중에 나와 있는 일반적인 탄소/흑연 재료의 대부분은 열간 압출 및 성형(냉간 또는 열간)에 의해 성형되며, 등방성 성형은 성형 성능이 뛰어난 방법입니다. 진동 성형은 일반적으로 중형 및 거친 구조 흑연을 제조하는 데 사용되며, 입자 크기는 0.5-2mm 사이이며 일반적으로 이중 구운 흑연화 제품이 지배적이며 밀도는 1.55-1.75kg/m3, 더 거친 입자, 더 거친 표면을 사용할 수 없습니다. 정밀 가공용. 주로 화학 산업 및 금속 제련에......

더 읽어보기